在供电设备中,PMOS 管常当做开关使用,如果负载是较大的容性负载,则在 PMOS 管开通瞬间,造成前级电源电压跌落。如下面的示例:

现象描述:

PMOS 管打开时,会使前级电源 VCC 电压跌落。VCC_3G 并联一个 1000uf 电容,初步判断是 mos 管开启瞬间充电电流引起,减小容值有比较小的改善,直接去掉后电压才不会跌落,但是这个储能电容又不能去掉,请问有无改进办法?

其实,解决这个问题的关键,就在于降低大容量电容的充电速度。总的来说,有以下办法:

- 在 1000uF 与 PMOS 管之间串联电阻或者在电容上面串联电阻;

- 在 PMOS 管之前增加串联电阻;

- 降低 PMOS 管的开通速度,包括在 GS 间并联电容或者在 GD 间并联电容;

接下来,依次详解这三种方法。

一、在 PMOS 管与电容之间串联电阻或者在电容上面串联电阻

这种方法,其实就是降低电容的充电电流,从而减小前级电源电压的跌落。根据串联电阻的位置不同,可以分为两种,如图 2 所示。

不管哪种,串联电阻均能够降低电容的充电速度,但是也相应的降低负载驱动能力。

二、在 PMOS 管之前增加串联电阻

这种方法,其实和上面的方法大同小异,其本质都是降低前级电源对电容的充电电流,电路及如图 3 所示。

其中,串联电阻大小以负载最大电流和 PMOS 管的最大允许电流的平均值而定。

关于功耗计算如下:

AO3401 最大可承受 30A 的脉冲电流,降额一半,以 15A 计。取样电阻阻值计算为:0.7V / 15A = 46.6mOhm,取 47mOhm 。电路进入稳态后,电流为 1A。取样电阻上功耗为 47 mW,与 MOS 管 (Ron = 50 mOhm) 相当。普通贴片电阻 0603 额定功率为 100 mW,仍有 50% 以上的降额幅度。

从仿真波形看,Q1 和 Q2 电流为 0 ,PMOS 管偏置由 C1 维持。

假设单片机控制电压为 5V,电源电压也为 5V。整个电路耗电 5V × 1A = 5W。

开关控制电路耗电为:

(47 + 50) mOhm × 1A + (5 – 0.7) V ^ 2 / 200 kOhm

= 97 mW + 92.45 mW = 189.45 mW

占约 0.18945 / 5 = 3.789% 的整个电路功耗。

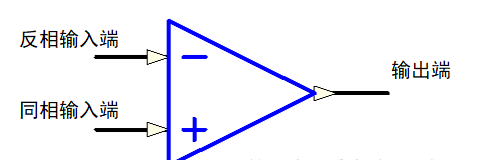

三、降低 PMOS 管的开通速度,GS 间并联电容或者在 GD 间并联电容

这种方法则是通过控制 PMOS 管的沟道宽度来间接控制电容的充电电流。同样,根据并联电容的不同位置,也有两种方法:

3.1 GS 间并联电容

S8050 三极管未导通时,并联电容两端电压均为前级电源电压;当 S8050 导通后,并联电容则通过 1.2K 电阻 R4 放电,也就是 PMOS 管的栅极电压,当 GS 电压(PMOS 管 S 大于 G)满足导通阈值时,PMOS 管开始逐渐导通。

这种方法的效果跟并联电容容值,放电电阻阻值,PMOS 管的 GS 开通阈值有关。例如,PMOS 关的 GS 开通阈值一定时,并联电容的容值越多,效果越好。

但是,这也是这种方法的缺点。

3.2 GD 间并联电容

S8050 三极管未导通时,并联电容两端电压分别为栅极 VCC,漏极为高阻态;当 S8050 导通后,并联电容开始通过电阻 R4 放电,PMOS 管栅极电压逐渐降低,PMOS 管逐渐导通,PMOS 管漏极电压升高,反过来会使与 PMOS 管栅极连接的并联电容的极板电压升高(并联电容放电电流流经 R4 的结果),又抑制 PMOS 管的开通,如此反复,可以使电容平稳充电。

这部分可以参考:AN1030 Design wiht MOSFET Load Switch