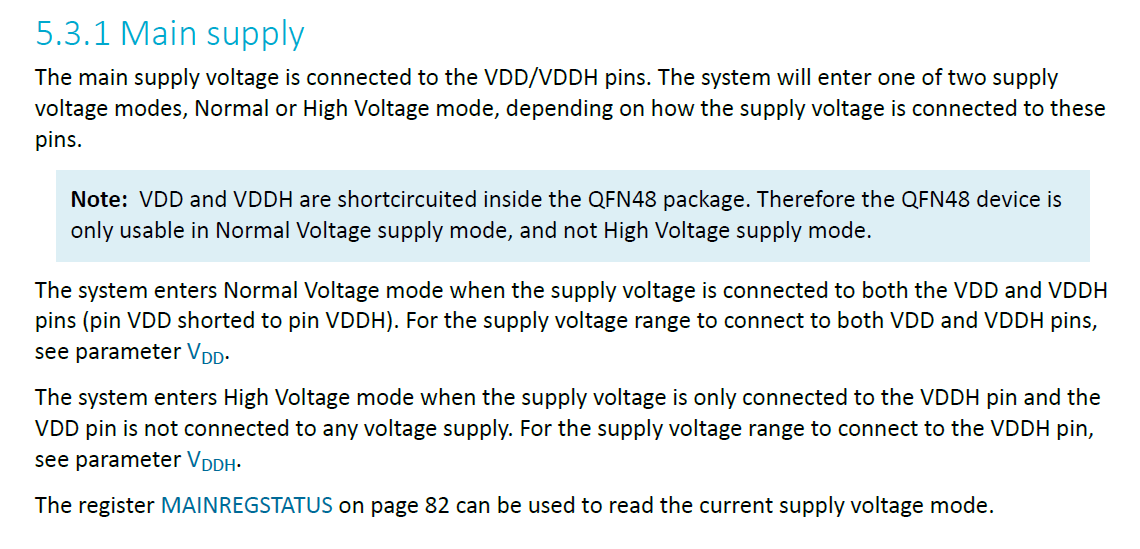

nRF52840芯片规格书中对于High Voltage mode和Normal Voltage mode的描述如下:

这里需要注意的是QFN48封装的nRF52840,即nRF52840 QFAx中是没有高电压模式的。

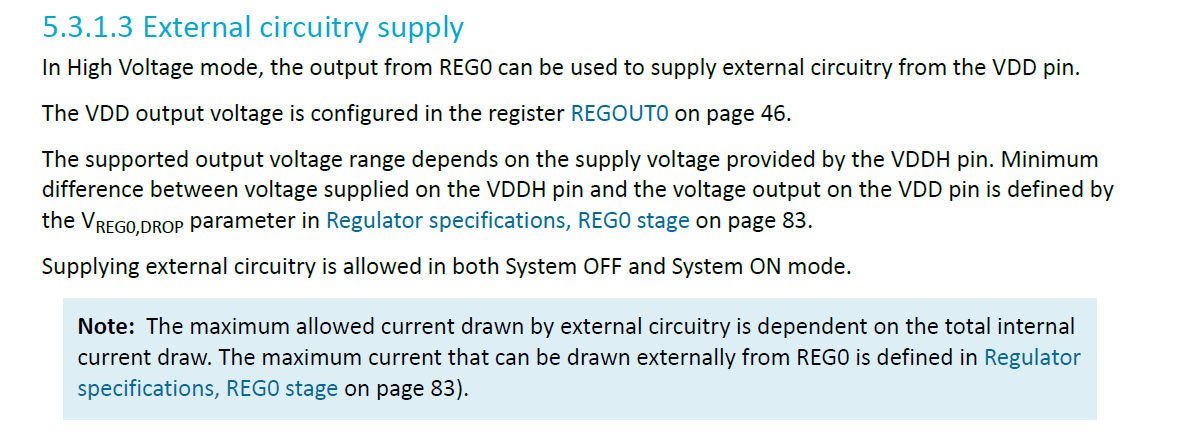

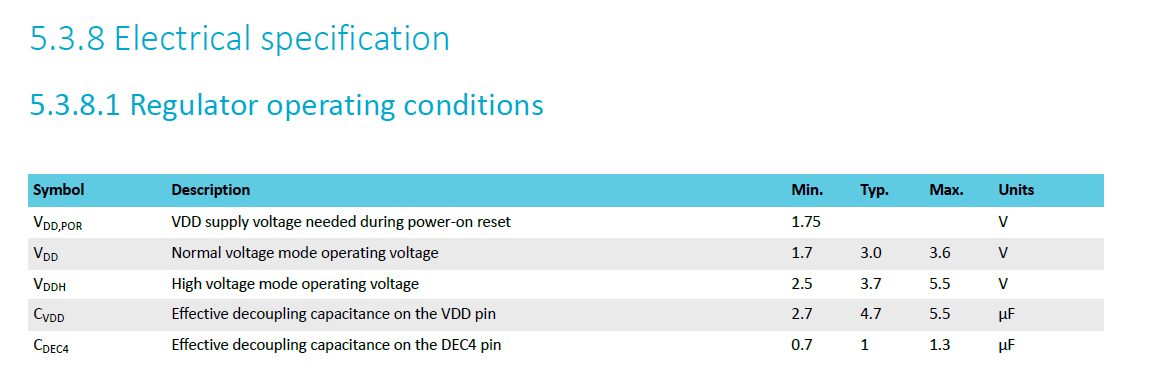

从规格书里可以看到NRF52840在高压模式下是支持将VDD当作Output来给其他设备供电,可以通过配置REGOUT0寄存器来配置特定电压

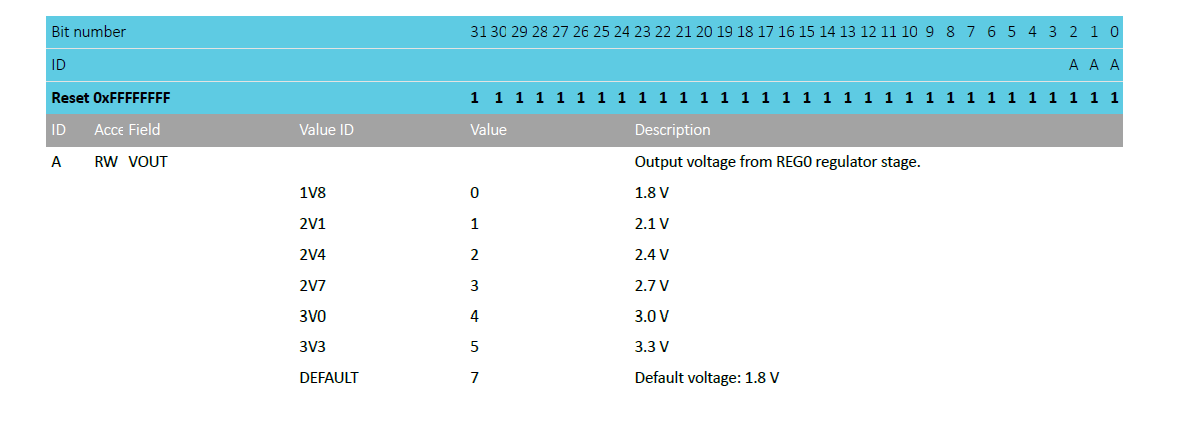

VDD支持的输出电压范围取决于VDDH引脚提供的电源电压。从规格书中可以看到VDDH与VDD的最小差值为0.3V,即当VDDH供电为3.6V时,VDD最大输出电压为3.3V。从下面这个表我们还可以看出,VDD最大的输出电流为25ma(发射功率小于4dBm时)。所以开发者在设计NRF52840的硬件时,如果是较简单的系统,如系统只有NRF52840和一个传感器,且系统由锂电池或USB供电,直接由NRF52840的VDD给传感器供电,但是需要注意传感器的峰值功耗不应大于下表。

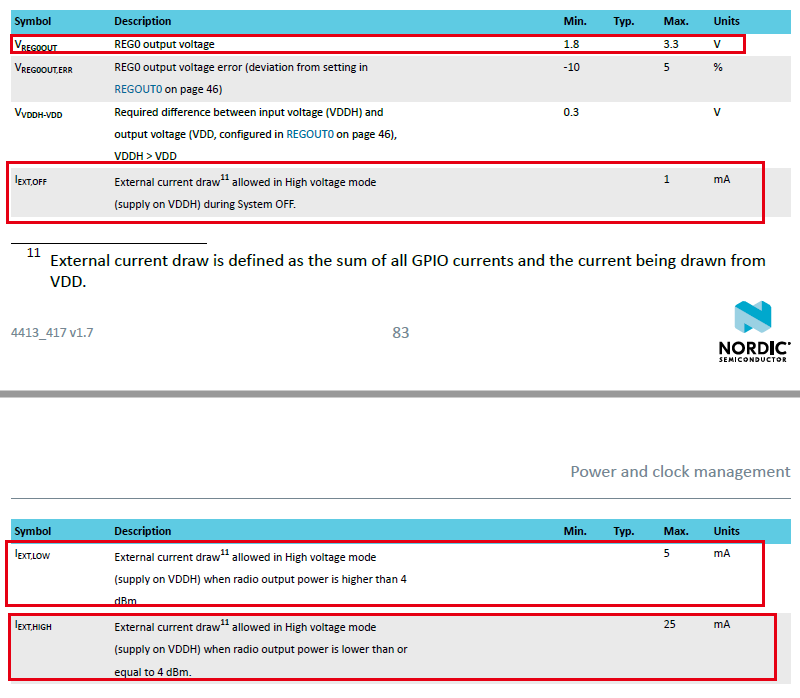

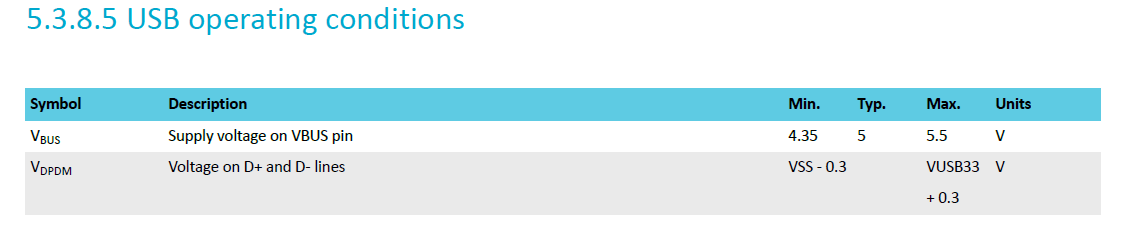

最后是电源脚供电电压的值的问题,如下表是NRF52840的VDD、VDDH、VBUS三个脚所支持的电压范围,此内容可以在规格书的Power and clock management一章中找到。

小结:此章节仅以nRF52840为例,不是所有Nordic芯片都支持高压模式与VDD External circuitry supply,切勿生搬硬套到其他型号的Nordic芯片。开发者在开发过程中需要阅读所选择芯片的规格书去做设计。此章节只是提供一个如何根据官方参考设计结合规格书做硬件设计的思路。

3、晶振选择

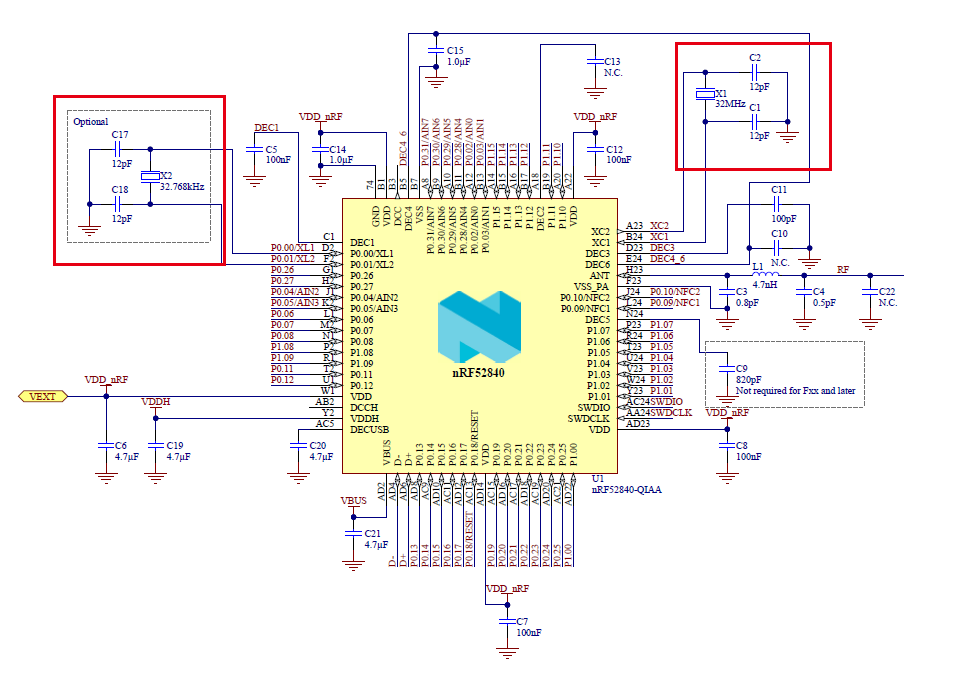

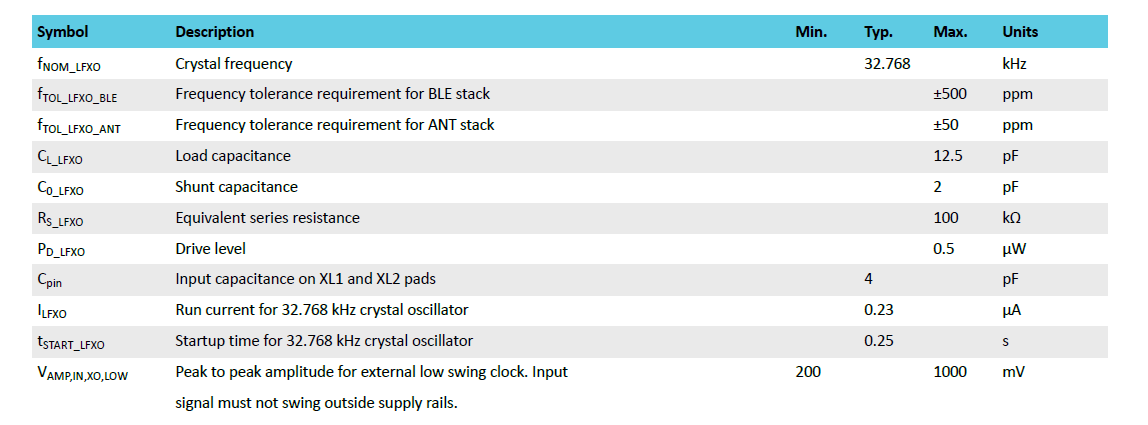

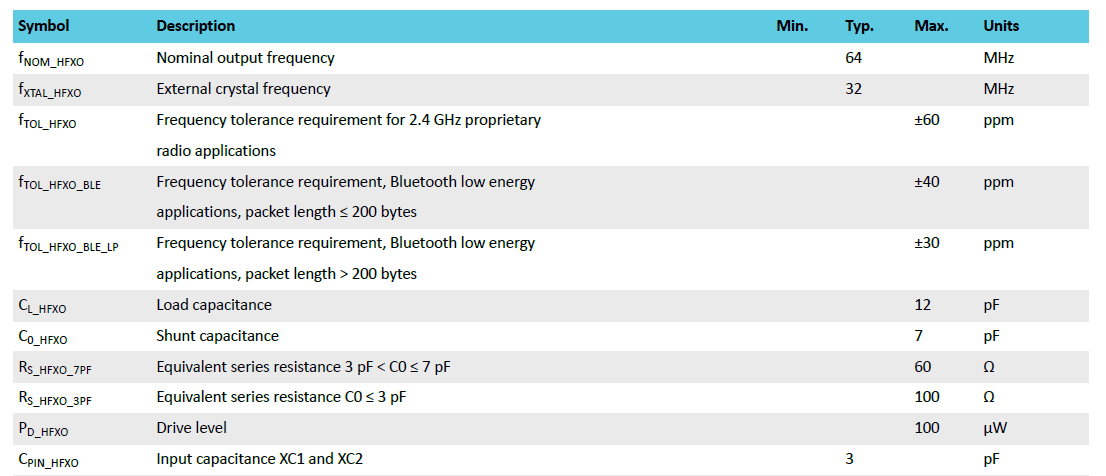

Nordic的芯片一般外围需要两颗晶振,一颗低频的32.768K,一颗高频的32M。低频晶振负载提供时钟源,高频晶振负载提供射频运行时的频率基准源。

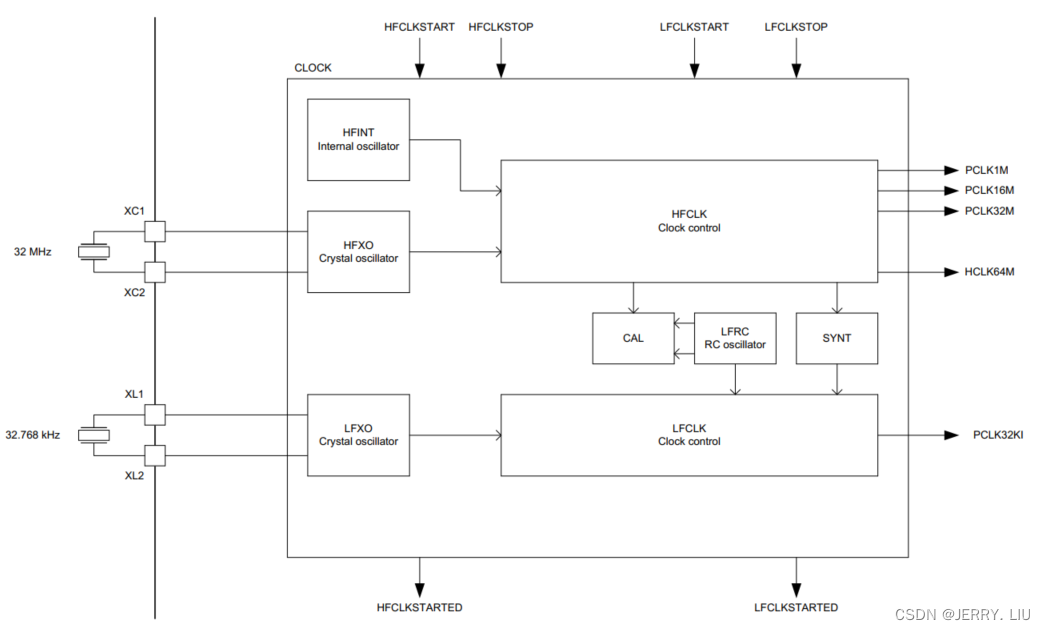

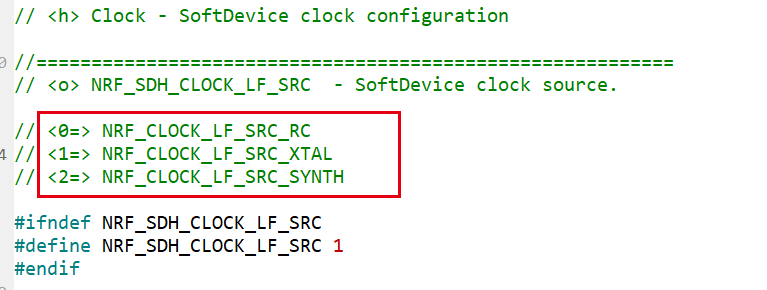

nRF52832有两频率的时钟,64MHz高速时钟和32.768kHz的低速时钟。这两个时钟可由以下电路产生,可通过配置config.h文件来软件选择各自的时钟源。

产生64MHz高速时钟的途径有两个:

(1)64MHz 片上时钟;

(2)用外部32MHz晶振产生64MHz时钟;

产生32.768kHz低速时钟的途径有三个:

(1)32.768KHz片上RC振荡器,精度为+/-250ppm.

(2)用外部32.768kHz晶振产生的32.768kHz的时钟;

(3)由64MHz的时钟综合而成的32.768kHz的时钟;

一般而言,内部的64MHz片上时钟的抖动较大不建议使用,无法满足2.4GHz BLE频率的PLL要求。所以在BLE中,高速时钟必须由外部32MHz晶振产生。

对于低速时钟,如果对时钟精度没有很高的要求,对于PCB面积受限的应用,可以选择使用内部RC,从而省掉外部的32.768K和负载电容。

两颗晶振的参数要求如下:

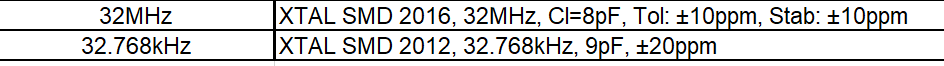

可以直接按照Nordic官方DK用的晶振参数去选型

4、LDO与DCDC供电模式选择

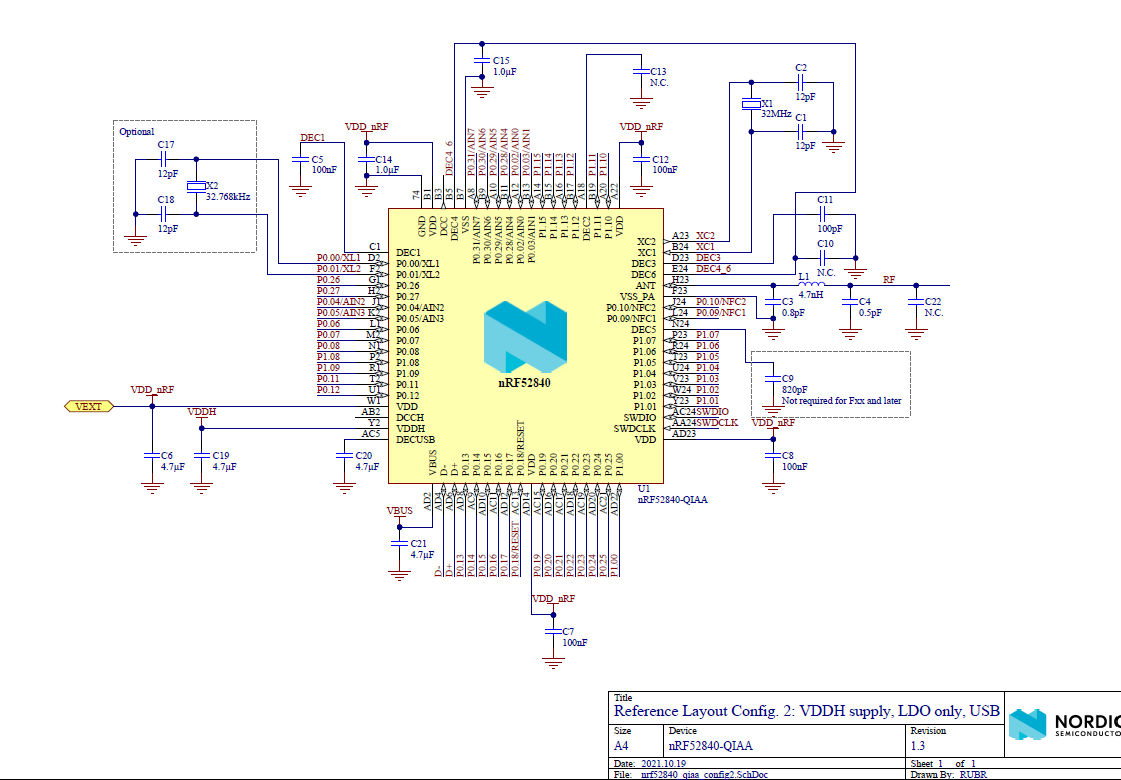

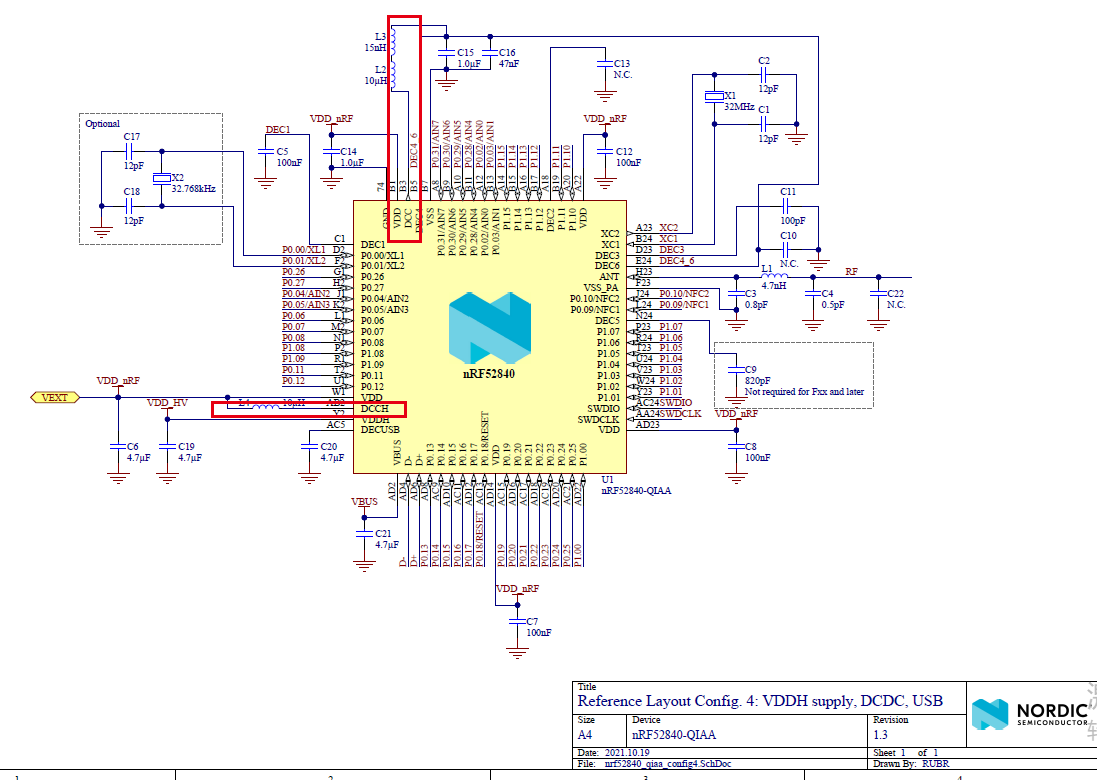

如下图是nrf52840_qiaa_config2和nrf52840_qiaa_config4参考设计的原理图,这两个参考设计都是用了高电压模式供电,但两者的区别是nrf52840_qiaa_config4的DCC脚和DCCH上接了电感。这里就要引入nRF51/52/53系列芯片的一个重要硬件概念:LDO和DCDC

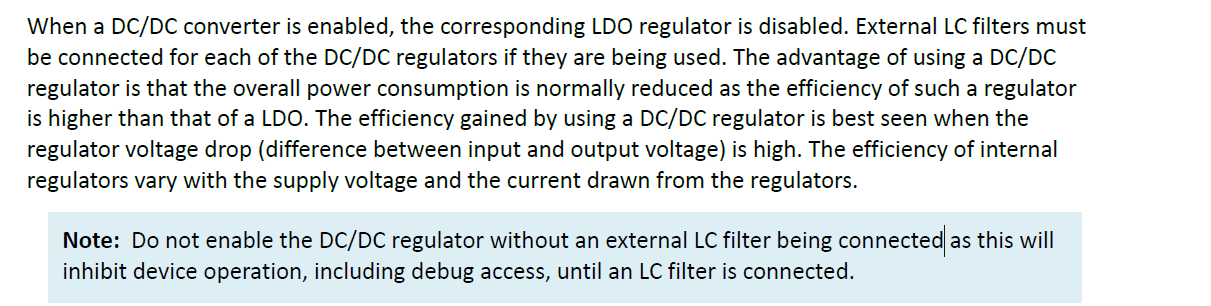

如下是规格书中芯片的LDO和DCDC模式的介绍,简单的概括就是DCDC模式的功耗会比LDO模式的功耗低

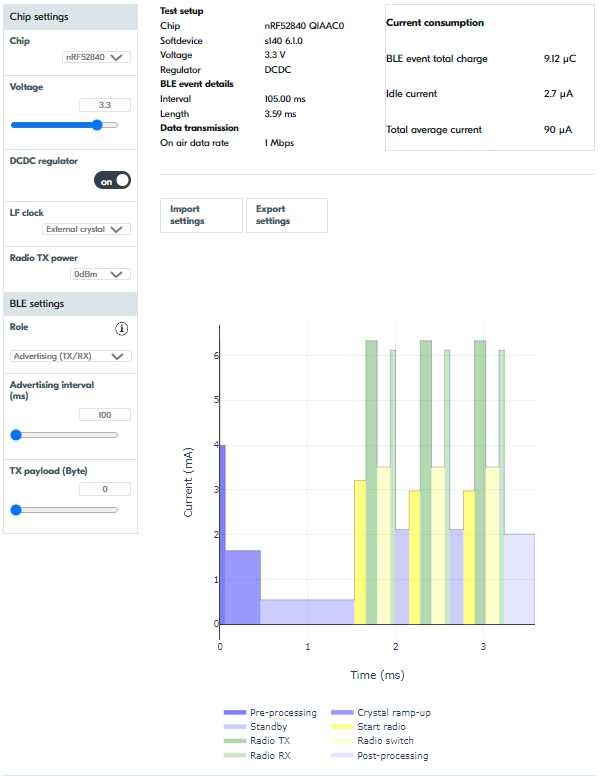

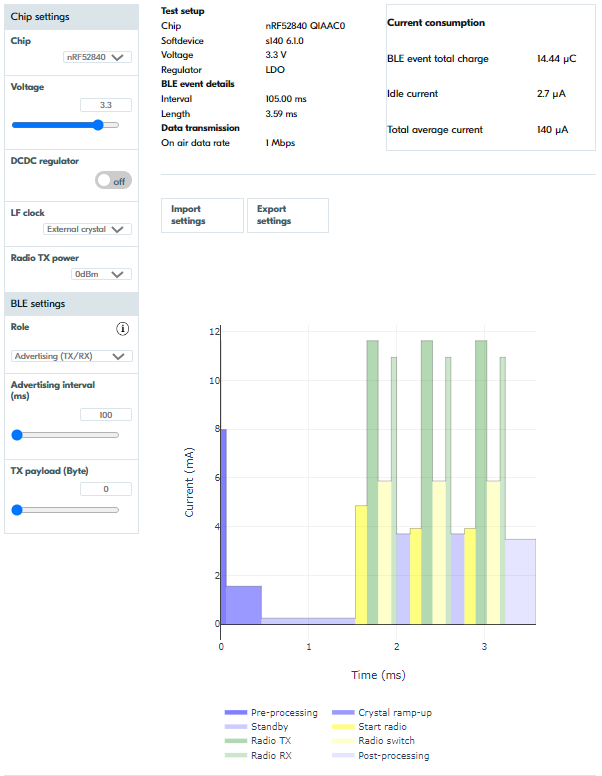

我们可以从Nordic官方给出的在线功耗评估工具来直观的看二者在功耗上的差距:https://devzone.nordicsemi.com/power/w/opp/2/online-power-profiler-for-bluetooth-le

从下面两张图可以看出,同样使用nRF52840,3.3V供电,发射功率为0dBm,使用外部低频晶振,设置广播周期为100ms的情况下,DCDC模式的平均功耗为90uA,而LDO模式的平均功耗为140uA。

5、GPIO的选择

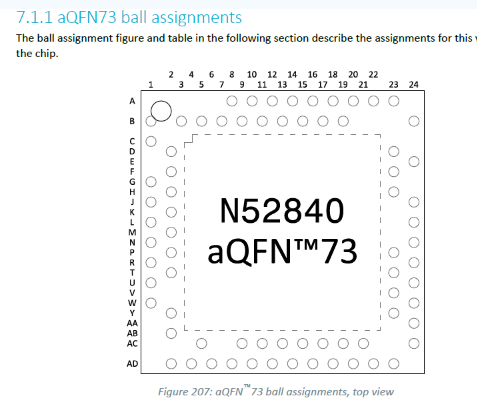

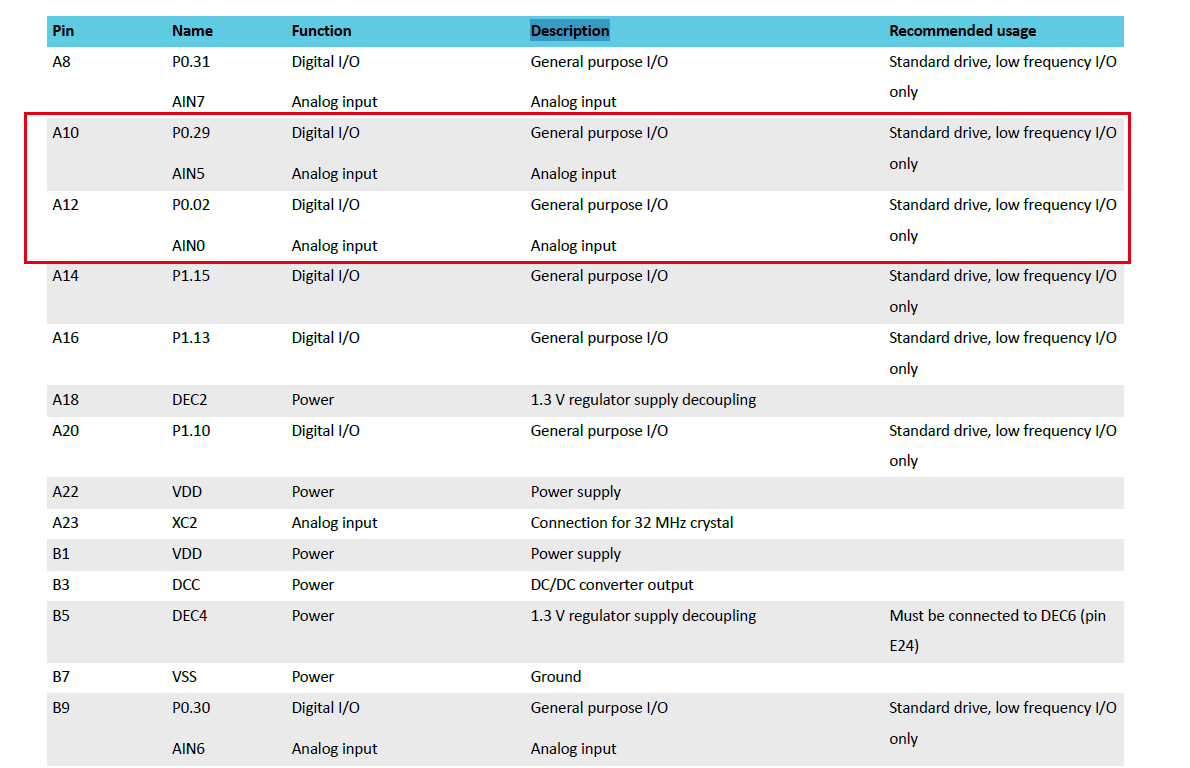

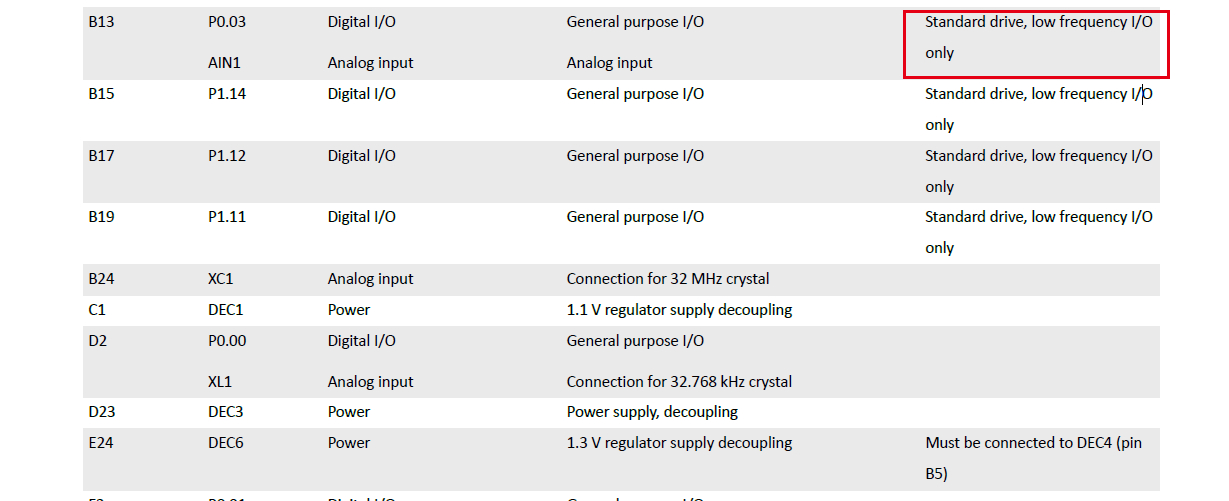

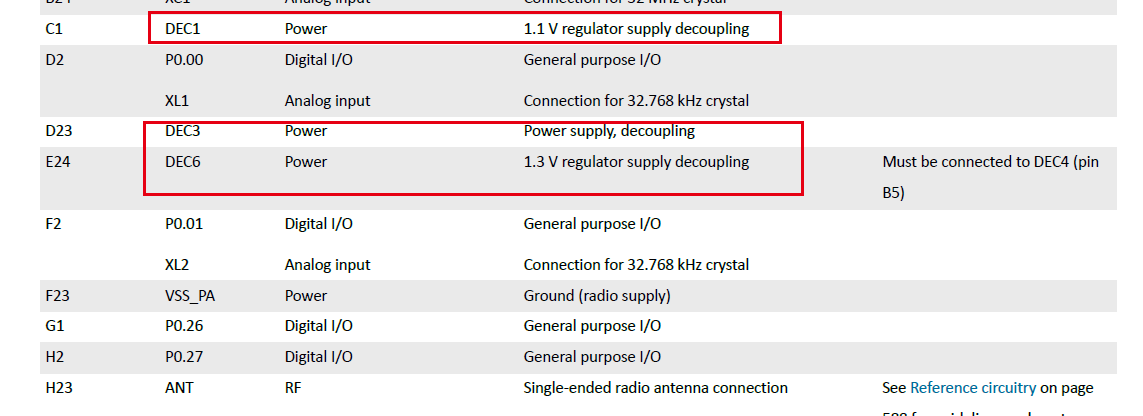

NRF51/52/53系列芯片的外设(除ADC、QSPI、HSPI)是可以在GPIO上自由映射的,没有限定特定的脚位,我们可以从芯片规格书中看到,以NRF52840 QIAA为例。可以从下表中看到部分GPIO的Description中标注了Analog input,这就是可以用做ADC的GPIO。

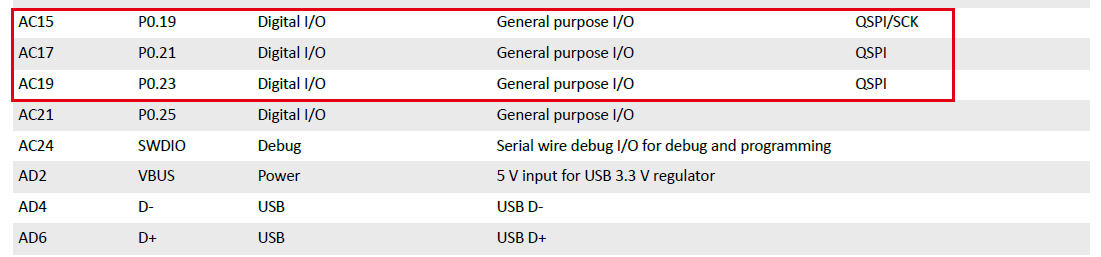

同样的QSPI脚在Recommended usage中也有标注出来

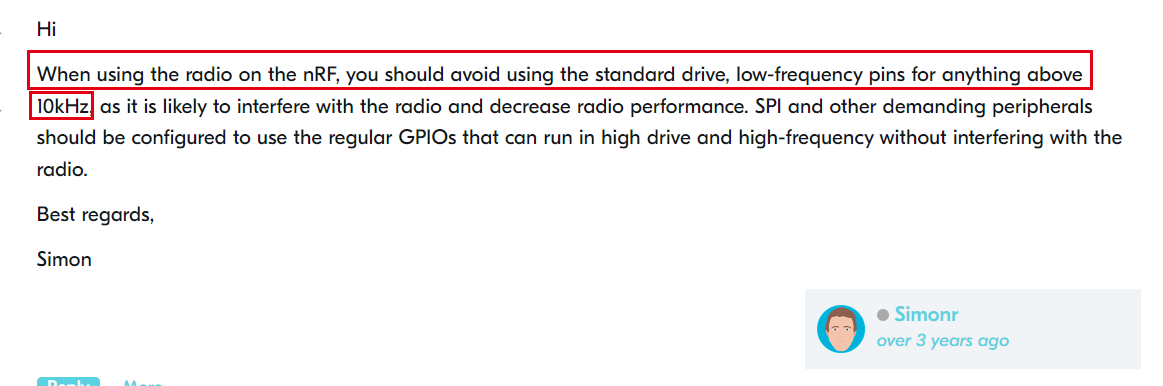

这里需要注意标注有 low frequency I/O only的GPIO。

关于此类GPIO,Noridc官方的描述是此类GPIO可以用做外设,但是在射频开启时不建议用做10KHz以上的外设,如UART、SPI、I2C、I2S等,射频开启的情况下用这些GPIO做高速外设会影响射频性能。

看到这里可能部分初学者会对芯片DEC脚的作用产生疑问。芯片带有DEC的脚位是芯片的退耦脚,需要外接退耦电容。退耦电容的接法和值在芯片的参考设计中已经给出,直接照搬参考设计即可。关于退耦电容的作用,感兴趣的读者可以自行搜索,简单来说,退耦电容是用来消除输入的电流在芯片中产生的震荡和自激电流用的。

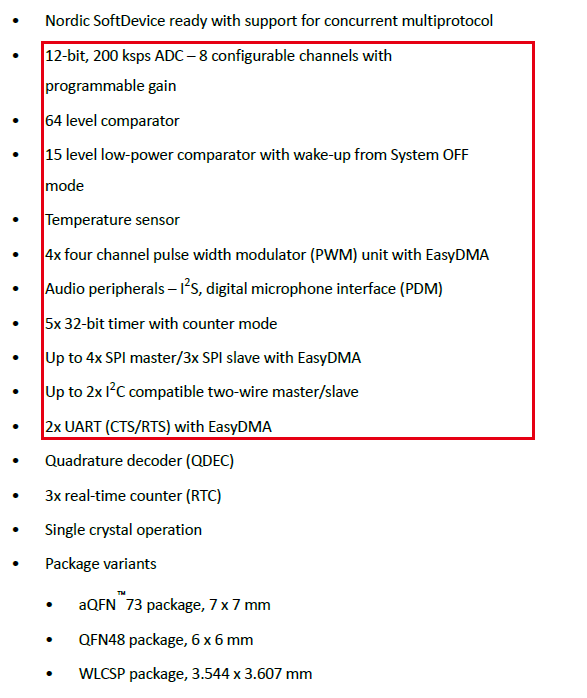

关于外设的类型和数量,可以在芯片规格书的首页看到,以NRF52840为例:

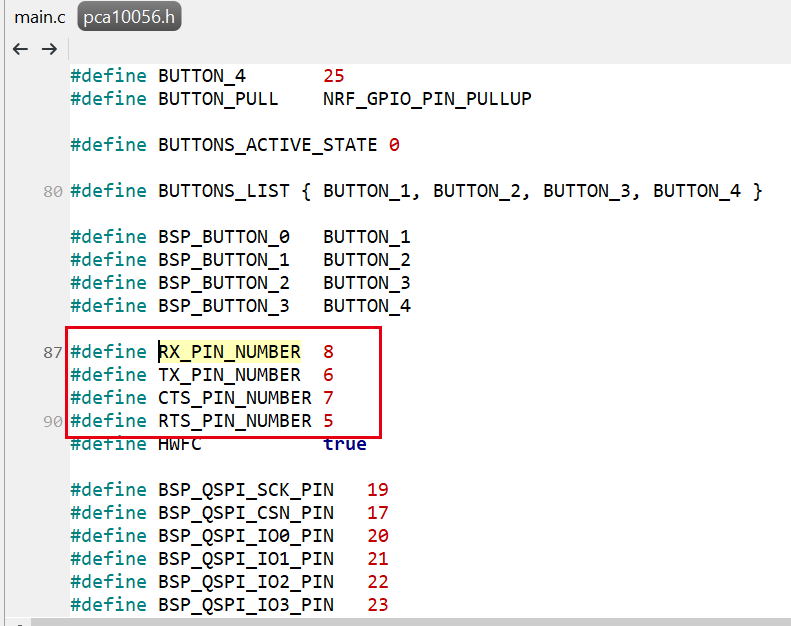

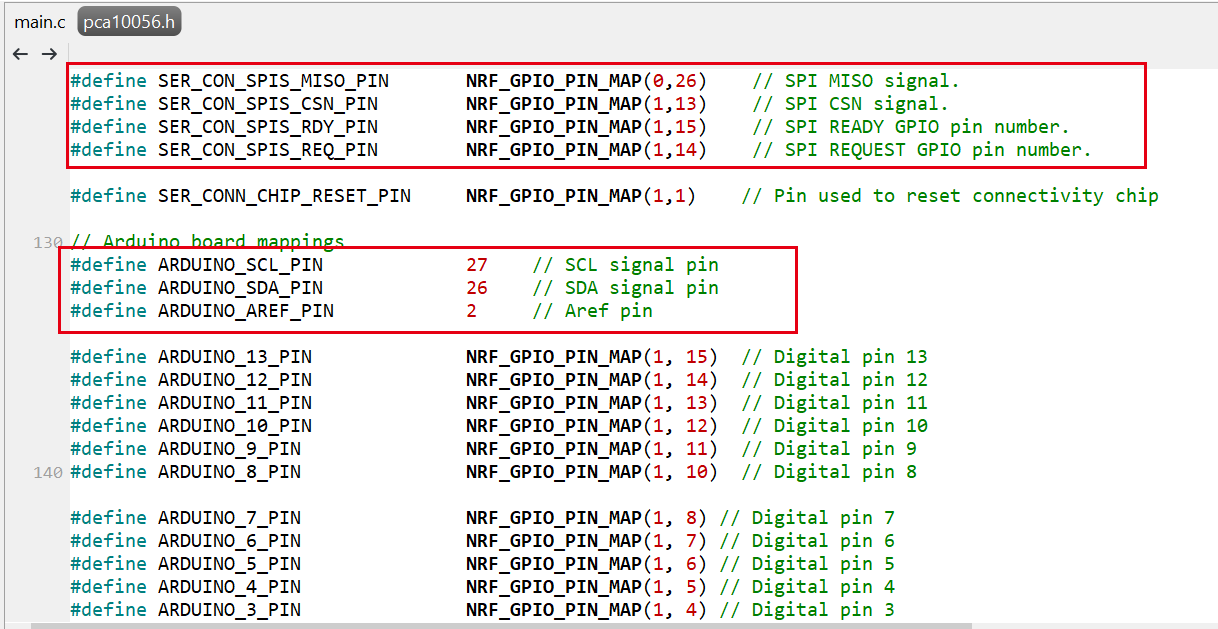

如果你对选择外设和GPIO有困难,也可以直接选择Nordic官方DK使用的外设接口,可以在SDK的PCA100xx.h文件夹中找到,继续以NRF52840为例,NRF52840对应的外设头文件为PCA10056.h

如果你选择的是其他的芯片,如NRF52832,去对应的PCA10040.h即可,下面是Nordic系列芯片对应的开发板名称

PCA10040对应NRF52832

PCA10010对应NRF52810

PCA10056对应NRF52840

PCA10056e对应NRF52811

PCA10010对应NRF52833

PCA10010e对应NRF52820

PCA10028对应NRF51422/51822/51802

6、GPIO电平问题

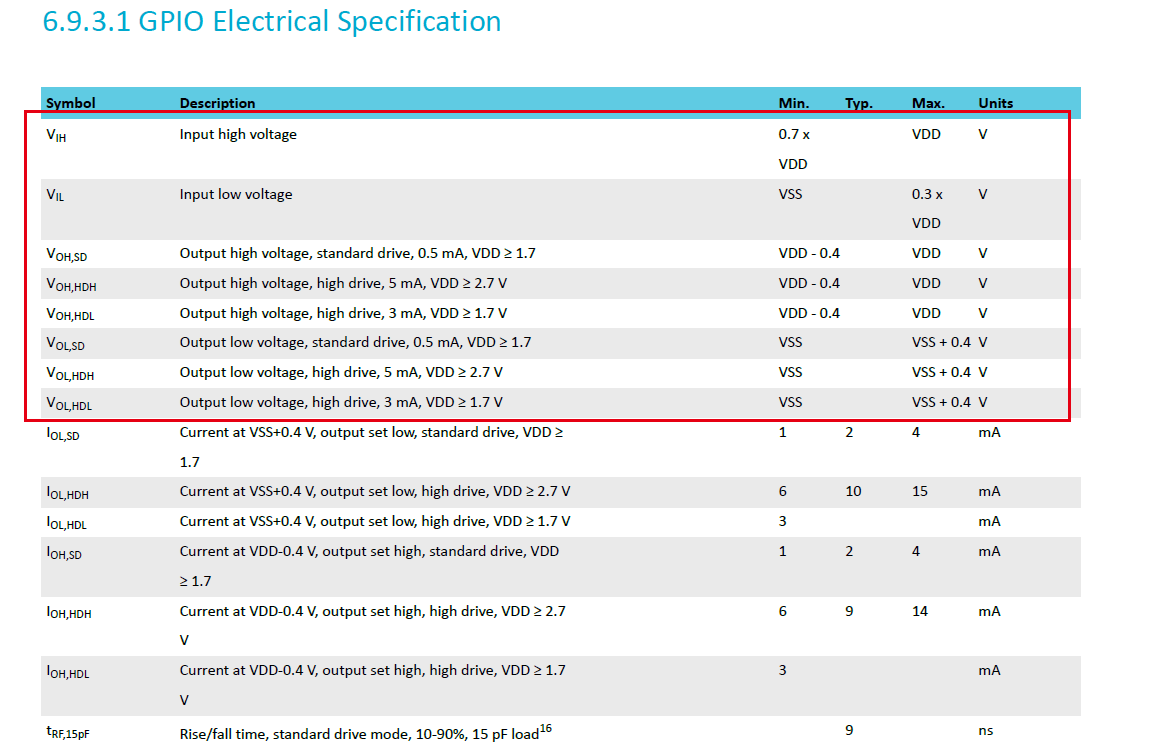

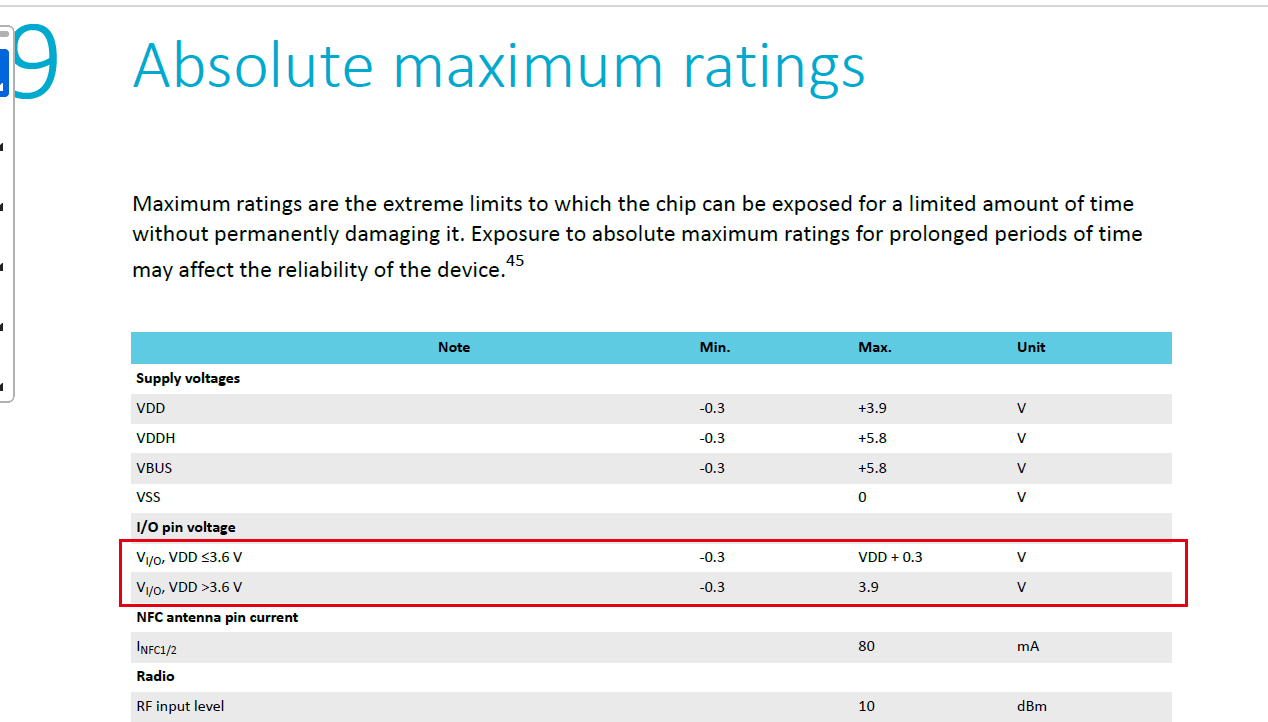

Nordic的芯片的GPIO电平与VDD有关,从下面两个图片中可以看到,VDD引脚供电的电压决定了GPIO电平的高电压。即如果VDD供电为3.3V,那么GPIO的输入/输出电平为3.3V,此时输入的最高电平不应超过3.3+0.3V,否则会造成GPIO永久损坏。

同理,如果接在Nordic芯片外部的传感器或其他模组/芯片为1.8V,那么只需要给VDD供电1.8V即可,此时GPIO输入/输出电平为1.8V,此时输入的最高电平不应超过1.8+0.3V。

其他电平与之同理。

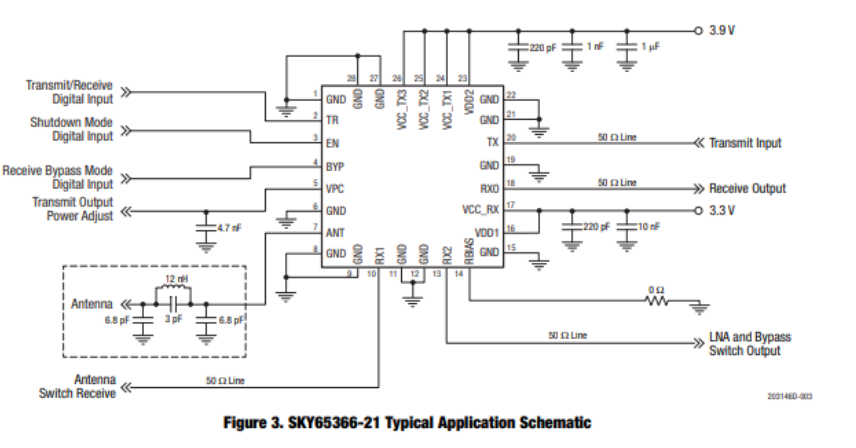

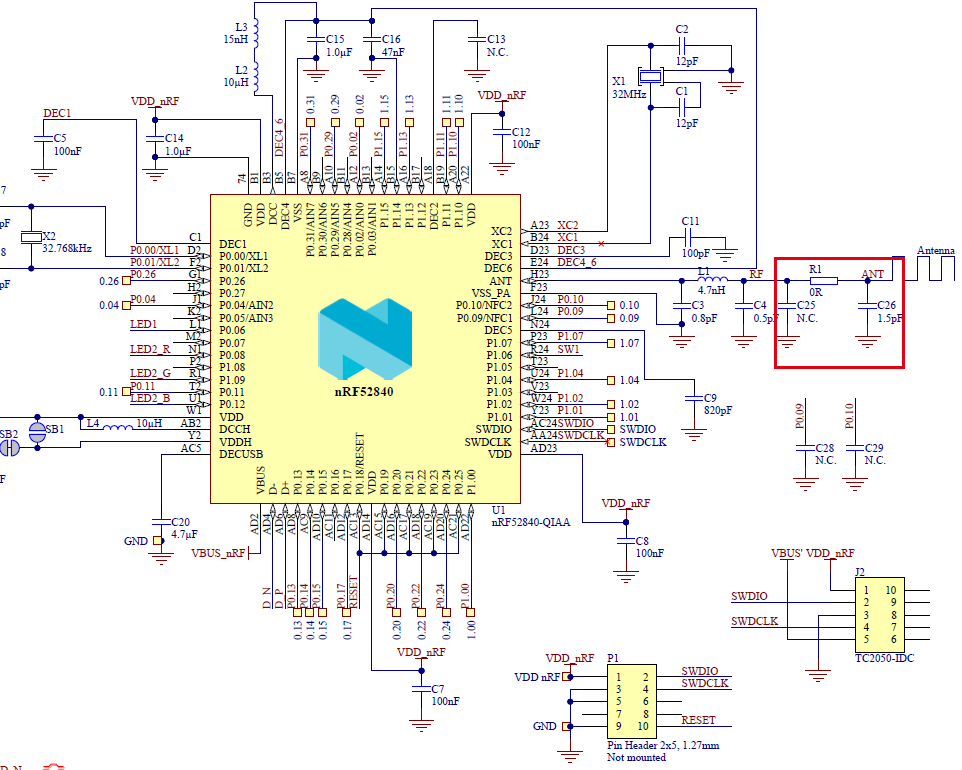

7、天线与匹配电路

按照Nordic给出参考设计,设计完最小系统,并选定外设的GPIO和供电电源之后,就剩下天线和匹配电路了。天线可以选择现成的2.4G陶瓷天线或是PCB天线,也可以以IPEX座的形式将天线引出到板外,使用体积更大的外接天线获得更好的信号。具体关于天线和匹配电路的问题,我会放在下一篇文章里面去详细讲。这里需要注意的是,Nordic给出的参考设计并没有预留天线的匹配电路,所以建议开发者在设计硬件原理图的时候,预留一个Π型匹配电路,方便后期调试天线。参考电路如下,R1、C25、C26共同组成了Π型匹配网络,初始值可以预留为R1=0R、C25=C25=N.C.。

总结:本文提供的是使用Nordic芯片做硬件设计的基本思路,按照上述步骤完成Nordic芯片的硬件设计之后,就可以进行下一步的Layout了。