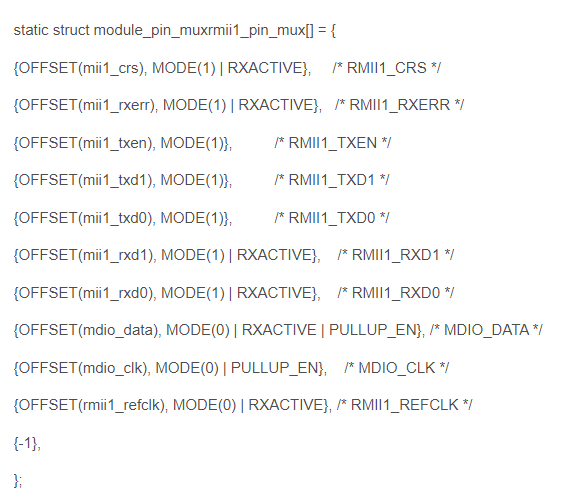

static struct module_pin_muxrmii1_pin_mux[] = {

{OFFSET(mii1_crs), MODE(1) | RXACTIVE}, /* RMII1_CRS */

{OFFSET(mii1_rxerr), MODE(1) | RXACTIVE}, /* RMII1_RXERR */

{OFFSET(mii1_txen), MODE(1)}, /* RMII1_TXEN */

{OFFSET(mii1_txd1), MODE(1)}, /* RMII1_TXD1 */

{OFFSET(mii1_txd0), MODE(1)}, /* RMII1_TXD0 */

{OFFSET(mii1_rxd1), MODE(1) | RXACTIVE}, /* RMII1_RXD1 */

{OFFSET(mii1_rxd0), MODE(1) | RXACTIVE}, /* RMII1_RXD0 */

{OFFSET(mdio_data), MODE(0) | RXACTIVE | PULLUP_EN}, /* MDIO_DATA */

{OFFSET(mdio_clk), MODE(0) | PULLUP_EN}, /* MDIO_CLK */

{OFFSET(rmii1_refclk), MODE(0) | RXACTIVE}, /* RMII1_REFCLK */

{-1},

};void enable_board_pin_mux(void)

{

......

// configure_module_pin_mux(rgmii1_pin_mux);

configure_module_pin_mux(rmii1_pin_mux);

......

}static struct cpsw_slave_datacpsw_slaves[] = {

{

.slave_reg_ofs = 0x208,

.sliver_reg_ofs = 0xd80,

.phy_addr = 0x00,

},

......

};int board_eth_init(bd_t *bis)

{

.......

writel((RMII_MODE_ENABLE| RMII_CHIPCKL_ENABLE), &cdev->miisel);

........

}Device Drivers ---> Networkdevice support ---> Ethernetdriver support ---> TexasInstruments (TI) devices -*- TI DaVinci MDIOSupport -*- TI DaVinciCPDMA Support TI CPSWSwitch Support [] TI CPSW Switchas Dual EMAC -*- PHY Device support and infrastructure ---> Drivers for SMSC PHYs

/* Module pin mux for rmii1 */

static struct pinmux_configrmii1_pin_mux[] = {

{"mii1_crs.rmii1_crs_dv",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_rxerr.mii1_rxerr",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_txen.mii1_txen",OMAP_MUX_MODE1 | AM33XX_PIN_OUTPUT},

{"mii1_txd1.mii1_txd1",OMAP_MUX_MODE1 | AM33XX_PIN_OUTPUT},

{"mii1_txd0.mii1_txd0",OMAP_MUX_MODE1 | AM33XX_PIN_OUTPUT},

{"mii1_rxd1.mii1_rxd1",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_rxd0.mii1_rxd0",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"rmii1_refclk.rmii1_refclk",OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLDOWN},

{"mdio_data.mdio_data",OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},

{"mdio_clk.mdio_clk",OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT_PULLUP},

{NULL,0},

};static void com335x_eth_init(void)

{

setup_pin_mux(rmii1_pin_mux);

am33xx_cpsw_init(AM33XX_CPSW_MODE_RMII, "0:00", NULL);

// intret = phy_register_fixup_for_uid(COM335X_EVM_PHY_ID, COM335X_PHY_MASK, am33xx_tx_clk_dly_phy_fixup);

}int am33xx_cpsw_init(enumam33xx_cpsw_mac_mode mode, unsigned char *phy_id0,

unsigned char *phy_id1)

{

......

#defineRMII1_IO_CLK_EN 1 << 6

gmii_sel |=(RMII1_IO_CLK_EN);

writel(gmii_sel,AM33XX_CTRL_REGADDR(AM33XX_CONTROL_GMII_SEL_OFFSET));

......

}Device Drivers ---> Networkdevice support ---> Ethernetdriver support ---> TexasInstruments (TI) devices -*- TI DaVinci MDIOSupport -*- TI DaVinciCPDMA Support TI CPSWSwitch Support TI CPSW Switchas Dual EMAC -*- PHY Device support and infrastructure ---> Drivers for SMSC PHYs

/* Module pin mux for rmii1 */

static struct pinmux_configrmii1_pin_mux[] = {

{"mii1_crs.rmii1_crs_dv",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_rxerr.mii1_rxerr",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_txen.mii1_txen",OMAP_MUX_MODE1 | AM33XX_PIN_OUTPUT},

{"mii1_txd1.mii1_txd1",OMAP_MUX_MODE1 | AM33XX_PIN_OUTPUT},

{"mii1_txd0.mii1_txd0",OMAP_MUX_MODE1 | AM33XX_PIN_OUTPUT},

{"mii1_rxd1.mii1_rxd1",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_rxd0.mii1_rxd0",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"rmii1_refclk.rmii1_refclk",OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLDOWN},

{"mdio_data.mdio_data",OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},

{"mdio_clk.mdio_clk",OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT_PULLUP},

{NULL,0},

};

/* Module pin mux for rmii2 */

static struct pinmux_configrmii2_pin_mux[] = {

{"gpmc_csn3.rmii2_crs_dv",OMAP_MUX_MODE2 | AM33XX_PIN_INPUT_PULLDOWN},

// {"gpmc_wpn.rmii2_rxerr",OMAP_MUX_MODE3 | AM33XX_PIN_INPUT_PULLDOWN},

{"gpmc_a0.rmii2_txen",OMAP_MUX_MODE3 | AM33XX_PIN_OUTPUT},

{"gpmc_a4.rmii2_txd1",OMAP_MUX_MODE3 | AM33XX_PIN_OUTPUT},

{"gpmc_a5.rmii2_txd0",OMAP_MUX_MODE3 | AM33XX_PIN_OUTPUT},

{"gpmc_a10.rmii2_rxd1",OMAP_MUX_MODE3 | AM33XX_PIN_INPUT_PULLDOWN},

{"gpmc_a11.rmii2_rxd0",OMAP_MUX_MODE3 | AM33XX_PIN_INPUT_PULLDOWN},

{"mii1_col.rmii2_refclk",OMAP_MUX_MODE1 | AM33XX_PIN_INPUT_PULLDOWN},

{"mdio_data.mdio_data",OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},

{"mdio_clk.mdio_clk",OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT_PULLUP},

{NULL,0},

};static void com335x_eth_init(void)

{

setup_pin_mux(rmii1_pin_mux);

setup_pin_mux(rmii2_pin_mux);

am33xx_cpsw_init(AM33XX_CPSW_MODE_RMII, "0:00", "0:01");

// intret = phy_register_fixup_for_uid(COM335X_EVM_PHY_ID, COM335X_PHY_MASK, am33xx_tx_clk_dly_phy_fixup);

}int am33xx_cpsw_init(enumam33xx_cpsw_mac_mode mode, unsigned char *phy_id0,

unsigned char *phy_id1)

{

......

#defineRMII1_IO_CLK_EN 1 << 6

#defineRMII2_IO_CLK_EN 1 << 7

gmii_sel |=(RMII1_IO_CLK_EN);

writel(gmii_sel,AM33XX_CTRL_REGADDR(AM33XX_CONTROL_GMII_SEL_OFFSET));

......

}

标签:

#AM335X#